芯片的“串联”本质已存在于内部结构

芯片并非单一元件,而是由数十亿晶体管、互连线及其他功能模块构成的微型系统,以手机处理器为例,其内部包含运算单元、缓存、控制模块等多个部分,这些模块通过精密布局与信号传输协同工作。这种高度集成化的设计本质上已实现“功能串联”——不同模块在统一架构下完成数据传递与处理,无需外部物理串联。

若强行将多个独立芯片串联,反而会破坏原有设计逻辑,两颗CPU直接串联会导致指令分配混乱,核心调度效率下降,现代芯片通过多核架构(如8核、16核)在单一晶圆上实现并行计算,既避免了串联带来的信号延迟,又降低了功耗与散热压力。

功耗与散热:串联的致命瓶颈

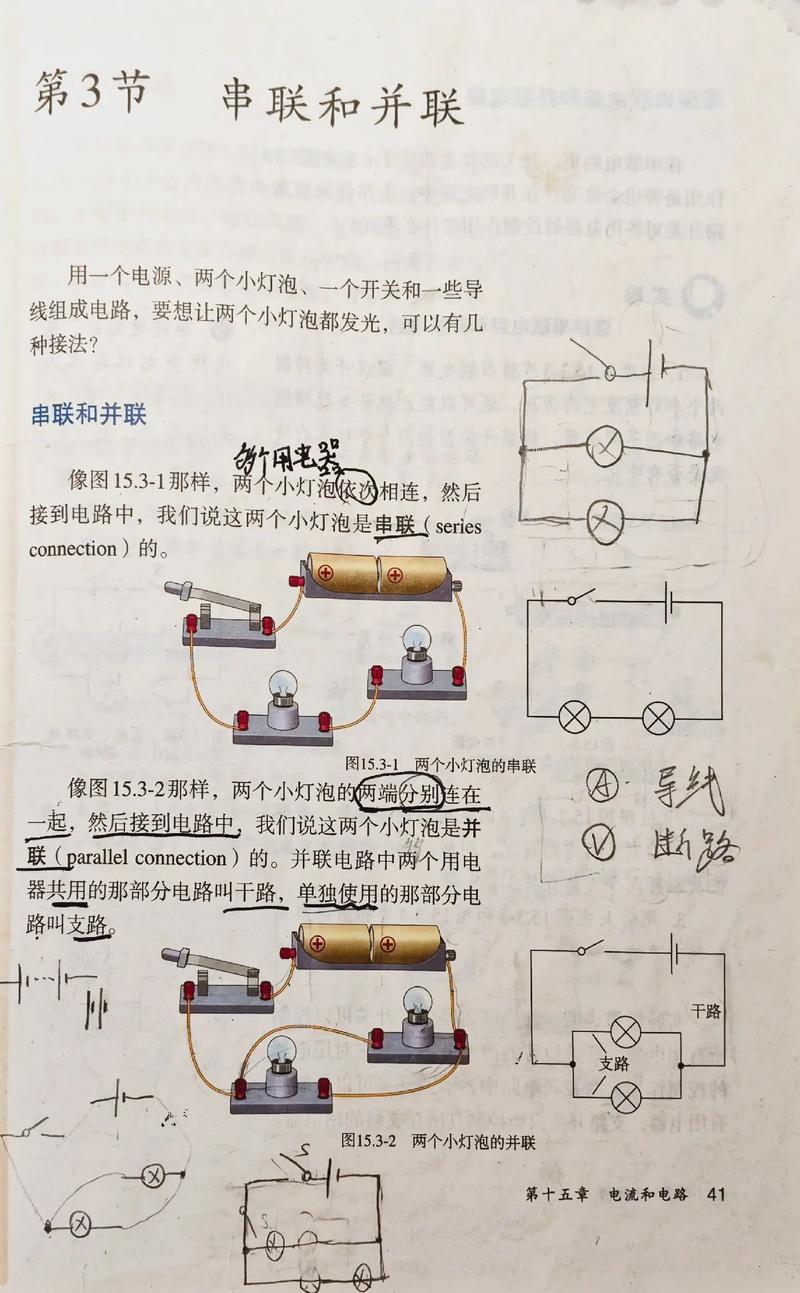

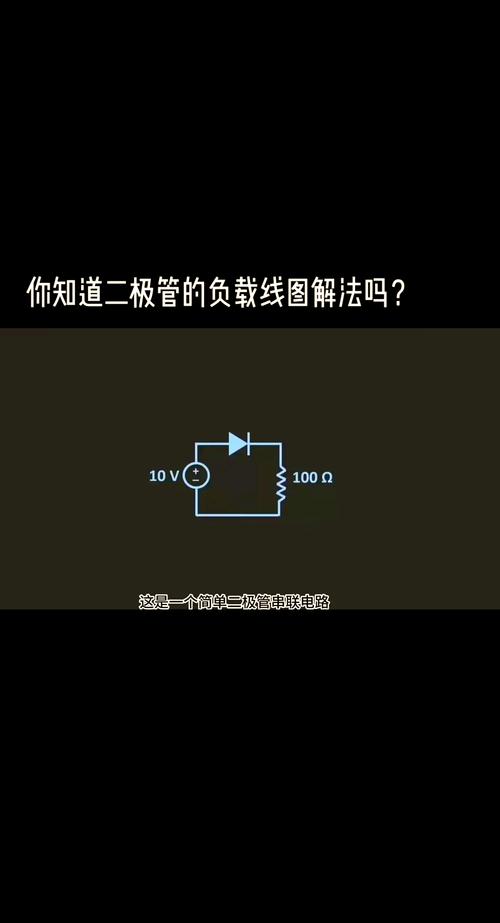

电子元件串联时,电流需流经每个节点,对于电阻这类简单元件,串联可均摊电压,但芯片的功耗特性截然不同,以7nm制程的芯片为例,其单颗功耗可能达到数十瓦,若两枚同规格芯片串联,总功耗将翻倍,但供电电压未必能同步提升。

更关键的是散热问题,芯片的发热密度极高,高性能计算芯片的局部温度可达80℃以上,若多颗芯片紧密串联,热量叠加会导致散热效率急剧下降,引发性能衰减甚至硬件损坏,这也是为什么服务器集群采用分布式散热设计,而非简单堆叠芯片。

信号同步与延迟的工程难题

芯片间数据传输依赖精确的时钟信号,当两颗芯片串联时,信号需经过外部接口(如PCB走线),这会引入额外延迟,以内存控制器与存储芯片的通信为例,即便是纳米级的时序偏差,也可能导致数据错误,现代DDR5内存通过“片上终端电阻”和“均衡信号技术”减少干扰,但这类优化仅适用于特定场景,无法解决多芯片串联的全局性时序问题。

相比之下,芯片内部通过光刻工艺实现的互连线长度可控,信号传输路径经过严格仿真,能最大限度降低延迟,苹果M系列芯片将CPU、GPU、内存整合为统一封装,正是为了规避外部串联的缺陷。

成本与可靠性的双重制约

半导体制造遵循“面积成本定律”——晶圆面积越大,良率越低,单个芯片成本呈指数级上升,若通过串联多个小芯片替代单颗大芯片,表面看可能节省成本,实则需额外投入接口电路、封装材料和测试流程。

串联设计会显著增加系统故障率,假设两枚芯片串联后整体可靠性为90%,每增加一枚芯片,可靠性将乘以自身良率(如90%×90%=81%),而单颗芯片可通过冗余电路(如ECC纠错)在相同面积内提升可靠性,无需承担串联带来的风险。

替代方案:先进封装与异构集成

行业早已探索出比串联更高效的技术路径。台积电的CoWoS封装、英特尔的Foveros 3D堆叠等技术,允许不同工艺的芯片通过硅中介层互联,在毫米级空间内实现超高带宽通信,AMD的Ryzen处理器将CCD(核心芯片)与IOD(输入输出芯片)分离,通过Infinity Fabric互连,既保持了模块化设计的灵活性,又避免了传统串联的缺陷。

Chiplet(芯粒)技术或将成为主流,通过标准化接口,不同功能的芯片像乐高积木一样组合,既能定制化满足需求,又可复用成熟设计,降低成本,这种“伪串联”模式本质上仍是并行架构的延伸。