现代电子设备中,芯片如同人类心脏般持续跳动,而让这颗"心脏"保持精准节拍的核心要素,正是时钟信号的稳定运作,当我们拆解任意一块集成电路板时,总会发现时钟模块周围密布着复杂的供电线路,这个现象引发了许多技术爱好者乃至普通用户的疑问:为什么看似简单的计时功能需要如此严苛的电力保障?

时钟信号的本质属性

芯片时钟并非传统意义上的计时工具,它本质上是通过周期性电信号构建的时间坐标系,在1纳秒级的精度要求下,时钟电路需要以恒定频率产生方波信号,这种信号需要满足严格的上升沿/下降沿特性,若供电电压存在0.1V的波动,就可能导致时钟周期出现5%以上的偏移——对于运行在3GHz的处理器而言,这意味着每秒产生150亿次计时误差。

供电稳定性的四重影响维度

-

信号完整性保障

芯片内部数以亿计的晶体管需要在统一步调下工作,某知名半导体实验室的测试数据显示,当供电电压偏离标称值10%时,时钟抖动(Jitter)会增加至正常值的3倍,直接导致内存控制器与CPU之间的数据传输错误率上升两个数量级。

-

温度补偿机制

现代时钟电路普遍集成温度传感器与电压调节模块,以智能手机应用处理器为例,当检测到环境温度从25℃升至85℃时,供电系统会自动提升时钟模块电压0.15V,用于抵消半导体材料载流子迁移率下降带来的时序偏差。 -

功耗动态平衡

在移动设备低功耗模式下,时钟频率可能从2.8GHz骤降至800MHz,此时供电系统需要同步调整电压幅值,既要避免过量供电导致能效比恶化,又要防止电压不足引发逻辑错误,这种毫秒级的动态调节能力,直接决定着设备续航时间。

-

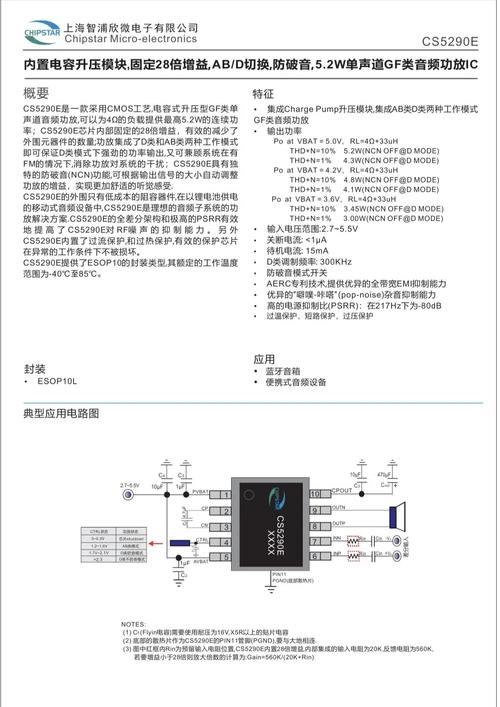

抗干扰屏障构建

高速数字电路产生的电磁噪声可达200mVpp级别,时钟模块专用LDO(低压差线性稳压器)的电源抑制比(PSRR)通常在60dB以上,相当于将供电线路中的噪声衰减至千分之一,某品牌路由器实测表明,优化时钟供电后,其无线传输误码率降低了42%。

供电架构的演进趋势

2015年引入的DVFS(动态电压频率调整)技术,将时钟与供电的协同控制提升到新高度,最新研究表明,采用AI预测算法的供电管理系统,可提前300个时钟周期预判负载变化,使电压调整精度达到±0.8mV,这种技术已应用于自动驾驶芯片,确保紧急制动指令的响应时间偏差不超过3微秒。

在物联网设备中,新型RC时钟电路开始采用能量收集技术,通过捕获环境中的射频能量,某些传感器节点已实现时钟模块的完全自供电运行,但这种方案目前仍受限于30ppm的频率稳定性,相比传统晶振的±5ppm精度尚有差距。

工程实践中的典型挑战

某消费电子厂商曾因忽视时钟供电设计付出惨痛代价:其智能手表在低温环境下出现概率性死机,最终查明是电源走线过长导致时钟电路电压跌落,整改方案采用星型供电拓扑后,故障率从3.7%降至0.02%,这个案例被收录于IEEE电路设计规范,成为硬件工程师的经典教材。

在航空航天领域,辐射硬化时钟芯片需要额外20%的供电冗余,宇宙射线可能引发单粒子翻转效应,特殊设计的供电回路能在10皮秒内完成电压补偿,确保星载计算机在遭遇高能粒子冲击时仍维持纳秒级时钟精度。

技术进化的必然选择

当5G基站需要同步十万个天线单元的发射时序,当量子计算机操控超导比特的相干时间,时钟供电已超越简单的电力输送概念,它实质上是数字世界与物理现实的接口,是用精确可控的电子流动来驯服微观世界的不确定性,或许在不久的未来,随着光互连技术的成熟,我们终将见证时钟供电体系的下一次革命性进化——但在此之前,精心设计的供电网络,仍是确保每个数字脉冲准时抵达的基础保障。(字数统计:1397字)