ic芯片为什么存在0扇区

在集成电路(IC)芯片的设计与功能实现中,"0扇区"是一个常被提及的概念,无论是存储类芯片(如EEPROM、Flash)还是安全类芯片(如智能卡芯片),0扇区的存在往往承载着关键的技术逻辑,对于普通用户而言,这一设计可能显得抽象,但理解其背后的技术原理,有助于更清晰地认识芯片的运行机制。

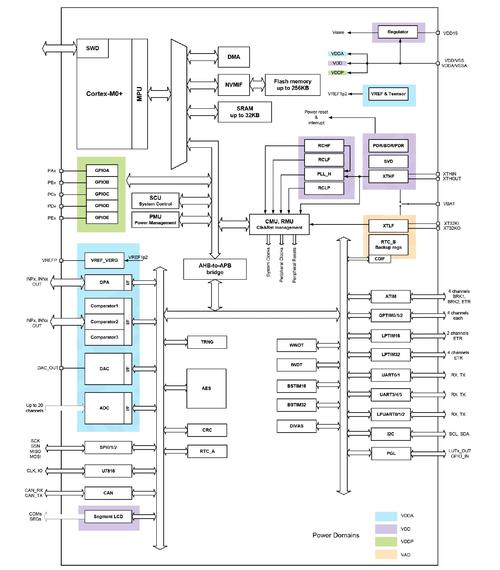

存储结构与扇区划分的逻辑

IC芯片的核心功能之一是数据存储与管理,无论是简单的数据记录,还是复杂的加密操作,都需要通过物理或逻辑上的分区来实现高效控制,扇区(Sector)作为存储单元的基本划分单位,其作用类似于书籍的章节——通过划分不同区域,芯片能够快速定位数据,并执行读写、擦除等操作。

0扇区通常被定义为芯片的“起始扇区”,从硬件层面来看,芯片的存储单元需要有一个明确的寻址起点,在Flash存储器中,地址0x00000000对应的物理位置即为0扇区的起始点,这种设计不仅符合计算机系统的二进制寻址习惯,还能简化控制器对存储单元的访问流程。

0扇区的核心功能与特殊性

0扇区并非普通的存储区域,其特殊性体现在以下几个方面:

-

固件与引导信息的存储

在多数芯片中,0扇区被预留用于存放固件程序或系统引导信息,微控制器(MCU)启动时,会优先从0扇区读取指令,初始化硬件并加载操作系统,这种设计类似于PC的BIOS,确保了芯片从“空白”状态到正常运行的可靠性。 -

安全芯片的密钥与权限控制

对于安全芯片(如智能卡、加密芯片),0扇区通常存储着核心密钥或访问权限表,MIFARE Classic卡的0扇区包含厂商信息与唯一标识符(UID),这些数据不可修改,且是后续认证流程的基础,这种设计既保障了芯片的唯一性,又防止了非法篡改。 -

容错与冗余设计的起点

现代芯片通常采用冗余存储技术,以提高数据可靠性,0扇区作为首个扇区,可能包含校验信息或备份指针,当其他扇区发生物理损坏时,控制器可通过0扇区的数据快速定位备用区域,从而降低整体故障率。

0扇区设计的底层逻辑

从技术实现角度,0扇区的存在与以下三个因素密切相关:

-

硬件寻址的天然起点

芯片的地址总线以二进制形式工作,地址0x00000000是唯一能被所有逻辑电路无歧义识别的起点,若从其他地址开始寻址,会增加电路设计的复杂度,并可能引发信号干扰问题。 -

标准化协议的要求

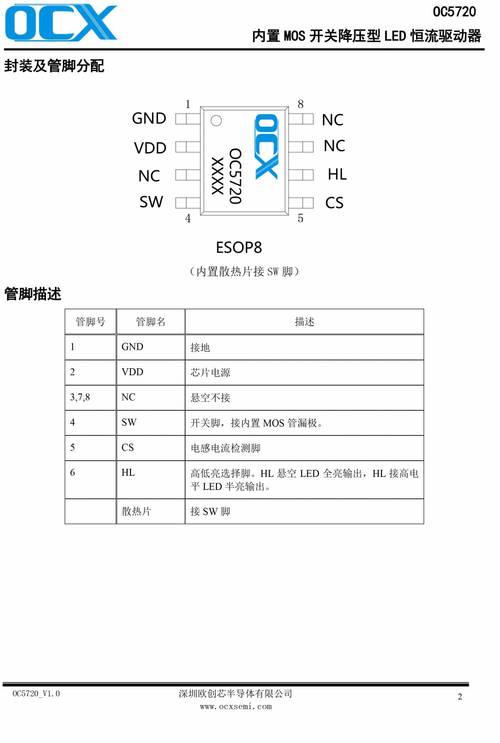

行业标准(如ISO/IEC 14443、JEDEC规范)对存储类芯片的分区方式有明确要求,在非易失性存储器中,0扇区必须包含设备ID和基础参数,以确保不同厂商的芯片能够兼容通用控制器。 -

安全防护的必要性

将关键数据置于0扇区,可借助物理防护机制(如熔丝锁、只读化设计)实现“硬件级保护”,攻击者若试图绕过0扇区直接访问其他区域,可能触发芯片的安全熔断机制,导致数据自毁。

0扇区在实际应用中的挑战

尽管0扇区的设计在技术上具有合理性,但其也存在一定的局限性:

- 写入次数的限制:频繁擦写0扇区可能导致存储单元寿命缩短,EEPROM的0扇区若用于记录动态日志,可能因擦写次数过多而提前失效。

- 兼容性问题:不同厂商对0扇区的定义可能存在差异,某款Flash芯片的0扇区包含坏块表,而另一款芯片可能将其用于存储校准参数,若开发者未仔细阅读芯片手册,可能导致初始化失败。

- 安全风险集中化:0扇区作为核心数据的存储区域,一旦被攻破,整个芯片的安全性将受到威胁,近年来,针对智能卡0扇区的侧信道攻击案例显著增加,进一步凸显了加固设计的必要性。

未来趋势与设计优化方向

随着芯片技术的迭代,0扇区的功能正在发生微妙变化:

-

动态化分区管理

部分新型芯片支持“虚拟扇区”机制,0扇区仅作为逻辑入口,实际物理地址可动态映射到其他区域,这种方式既能保留传统设计习惯,又可提升存储单元的利用率。 -

增强型安全方案

通过在0扇区集成物理不可克隆函数(PUF)或量子随机数发生器,芯片厂商可进一步提升密钥的不可复制性,即使攻击者获取了0扇区的数据,也无法在外部环境中复现有效信息。 -

AI驱动的故障预测

结合机器学习算法,芯片控制器可实时监测0扇区的健康状态,并提前预警潜在故障,通过分析擦写操作的电流波形,预测存储单元的寿命衰减趋势。